Samsung testet Exynos-Prozessor auf 1,4-Nanometer-Technologie mit 96 MB Cache und höheren Taktraten

50 % Plausibel Quelle: 3/5 Bestätigung: 1/5 Technische Bewertung: 3/5 Zeitplan: 3/5 Der 2-nm-GAA-Prozess wird noch einige Iterationen benötigen, bis Samsung Vertrauen in seine fortschrittliche 1,4-nm-Lithografie hat; dies bedeutet jedoch nicht, dass das Unternehmen nicht bereits frühzeitig Tests seines nächsten Exynos-SoC auf dem neueren Fertigungsprozess beginnen kann.

Kurzfassung

Warum das wichtig ist

- 50 % Plausibel Quelle: 3/5 Bestätigung: 1/5 Technische Bewertung: 3/5 Zeitplan: 3/5 Der 2-nm-GAA-Prozess wird noch einige Iterationen benötigen, bis Samsung Vertrauen in seine fortschrittliche 1,4-nm-Lithografie hat; dies bedeutet jedoch nicht, dass das Unternehmen nicht bereits frühzeitig Tests seines nächsten Exynos-SoC auf dem neueren Fertigungsprozess beginnen kann.

- Erste Spezifikationsdetails zeigen, dass Samsung eine neue Obergrenze für Taktraten einführen wird, nicht zu vergessen den System-Level-Cache (SLC), der auf beachtliche 96 MB erweitert wurde.

- Der Exynos 2700 ist noch nicht veröffentlicht, doch @SPYGO19726 hat bereits einige aussagekräftige Details zum ersten 1,4-nm-SoC des südkoreanischen Riesen geteilt, obwohl Gerüchte kursieren, Samsung habe Schwierigkeiten mit dieser Technologie, was dazu geführt habe, dass er sich auf den 2-nm-Prozess verlagert und dabei mehr Wert auf Ausbebestabilität legt als auf den Wettbewerb mit TSMC.

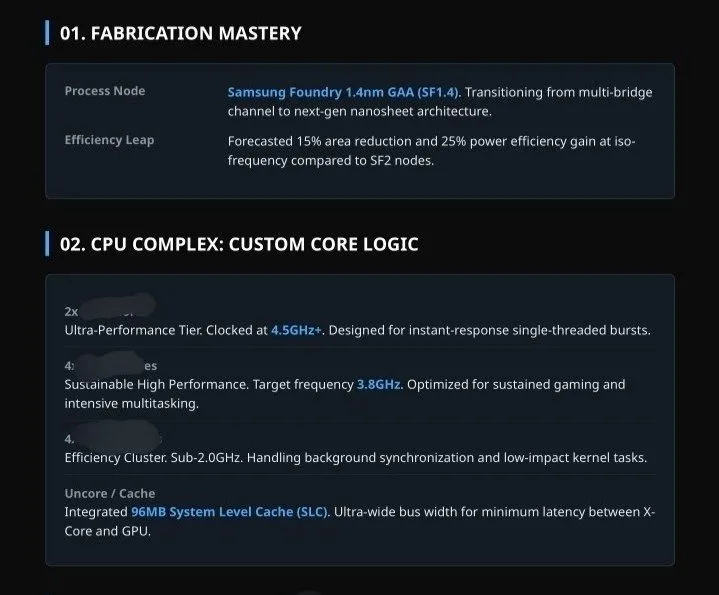

Die ersten Details deuten jedoch darauf hin, dass der neue Exynos, der auf dem 1,4-nm-Prozess getestet wird, über eine 10-Kern-CPU-Cluster-Architektur verfügt, die in einer „2 + 4 + 4"-Konfiguration angeordnet ist. Die beiden Prime-Kerne arbeiten mit 4,50 GHz, die Performance-Kerne mit 3,80 GHz und vier Effizienzkerne mit 2,00 GHz.

Doch das beeindruckendste Detail des unbekannten Exynos-SoC ist sein integriertes System-Level-Cache (SLC) mit 96 MB; auch @SPYGO19726 erwähnt eine ultrabreite Busbreite zur Minimierung der Latenz zwischen den CPU-Kernen und der GPU. Der SLC senkt die Speicherverzögerung und erhöht die Bandbreite, indem er häufig genutzte Daten im Cache speichert.

Je größer dieser Cache ist, desto schneller und effizienter läuft das Gesamtsystem, da Komponenten wie CPU, GPU, NPU, ISP und andere nicht ständig aktiv sein müssen, um Daten an den großen Cache zu senden. Leider hat der SLC den Nachteil, dass er einen erheblichen Teil der Siliziumfläche einnimmt, und je größer der Chip ist, desto teurer wird die Massenproduktion des Chipsatzes.

Es ist wichtig zu bedenken, dass die größte SLC-Cache in Smartphone-Chipsatz 10 MB beträgt und im Dimensity 9500 verbaut ist; eine Erhöhung auf 96 MB würde Samsung zwingen, eine Chipgröße zu entwickeln, die mit Smartphone-Formfaktoren unvereinbar wäre.

Zum Glück gibt es weitere Anwendungsbereiche, für die diese Technologie genutzt werden kann, doch da es sich lediglich um die ersten Spezifikationen handelt – wie beeindruckend diese auch sein mögen – müssen wir sie vorerst mit einer Prise Salz betrachten. Quelle: @SPYGO19726 Über den Autor: Omar Sohail ist Reporter und Analyst für die mobile Sektion Technologie und Geschäft der Mobilindustrie.

Seine Expertise liegt in der komplexen Hardware-Lieferkette, wobei er Entwicklungen in der Halbleiterfertigung, Chip-Lithografie und Kamerasensortechnologie abdeckt. Sie Wccftech auf Google, um weitere unserer Nachrichtenabdeckungen in Ihren Feeds zu erhalten.

Quelllink

Wccftech - Originalartikel oeffnenThema weiterverfolgen

Interne Verlinkung

Im Kontext weiterlesen

Diese weiterfuehrenden Links verbinden das Thema mit relevanten Archivseiten, Schlagwoertern und inhaltlich nahen Artikeln.

Technologie Archiv

Weitere Meldungen aus derselben Hauptkategorie.

Mehr von Wccftech

Alle veroeffentlichten Inhalte derselben Quelle im Archiv.

iPhone 18 Pro: Tipster zerstreiten sich über Dynamic Island, während Apple Chinas BOE von Displayaufträgen ausschließt

Redaktionell verwandter Beitrag aus dem selben Themenumfeld.

Neues MajorDoMo-RCE-Schwachstelle gefährdet Server mit Code-Executions-Angriffen

Redaktionell verwandter Beitrag aus dem selben Themenumfeld.

Quellenprofil

Quelle und redaktionelle Angaben

- Quelle

- Wccftech

- Originaltitel

- Samsung Testing Its Next-Generation Exynos On The 1.4 nm Process, Initial Specifications Boast 96MB Of Cache, Higher Clock Speeds & More

- Canonical

- https://wccftech.com/next-generation-exynos-tested-on-1-4nm-process-reveals-96mb-slc-cache-and-more/

- Quell-URL

- https://wccftech.com/next-generation-exynos-tested-on-1-4nm-process-reveals-96mb-slc-cache-and-more/

Aehnliche Inhalte

Verwandte Themen und interne Verlinkung

Weitere Artikel aus aehnlichen Themenfeldern, damit Leser direkt im selben Kontext weiterlesen koennen.

iPhone 18 Pro: Tipster zerstreiten sich über Dynamic Island, während Apple Chinas BOE von Displayaufträgen ausschließt

Das Apple iPhone 18 Pro wird nun weithin erwartet, ein leistungsfähigeres Display erhalten, wodurch Chinas BOE um die proverbialen Krümel kämpft.

06.05.2026

Live Redaktion

Neues MajorDoMo-RCE-Schwachstelle gefährdet Server mit Code-Executions-Angriffen

Ein kürzlich offengelegter Schwachstelle ermöglicht Angreifern, MajorDoMo-Server, die über Internet erreichbar sind, ohne Authentifizierung ferngesteuert Code auszuführen.

06.05.2026

Live Redaktion06.05.2026

Live RedaktionTaiwan-Hochgeschwindigkeitsbahn: Radio-Spoofing-Angriff stoppt drei Züge

Am letzten Tag Qingming-Festivals wurden drei Hochgeschwindigkeitszüge Taiwan-Hochgeschwindigkeitsbahn aufgrund eines ausgeklügelten Radio-Signal-Spoofing-Angriffs gezwungen, Notbremsungen durchzuführen.

06.05.2026

Live Redaktion